CHIPOLY

Curator-LCM

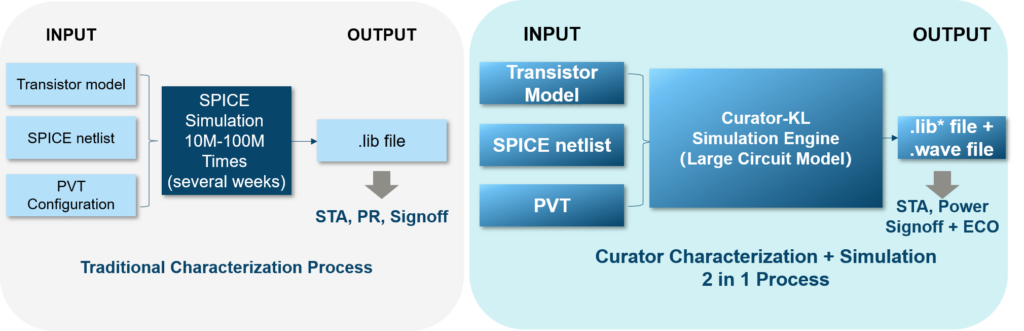

Next-generation Characterization + Simulation "2 in 1" Engine

Library Characterization + Circuit Simulation

Most of the chip area is dedicated to digital logic, memory, I/O, and customized IP implemented through static timing analysis-based digital methods. Therefore, efficient and accurate device characterization under all expected process, voltage, and temperature (PVT) conditions is crucial for whole-chip or block-level design flows. KL proposes using machine learning methods to generate feature libraries for any PVT conditions within a limited time frame, achieving modeling speeds for new corners that are more than ten times faster than traditional algorithms.

RUN TIME

Characterizing a new library typically requires millions of simulations, which can take several weeks to months to complete.

Arbitrary PVT

Obtaining specific PVT Liberty models can be prohibitively expensive, whether sourced from a fabrication facility or generated internally.

Traditional

EDA’s

Bottleneck

EDA’s

Bottleneck

Precise

Partial characterization and interpolation can partially achieve characterization. However, this approach may lead to potential timing or functional errors.

Verification & debug

The previous generation of Liberty validation tools conducted rule-based static checks, only able to detect certain types of content inconsistencies.